Hdl Design Flow

Schematic based hardware description language and combination of both etc.

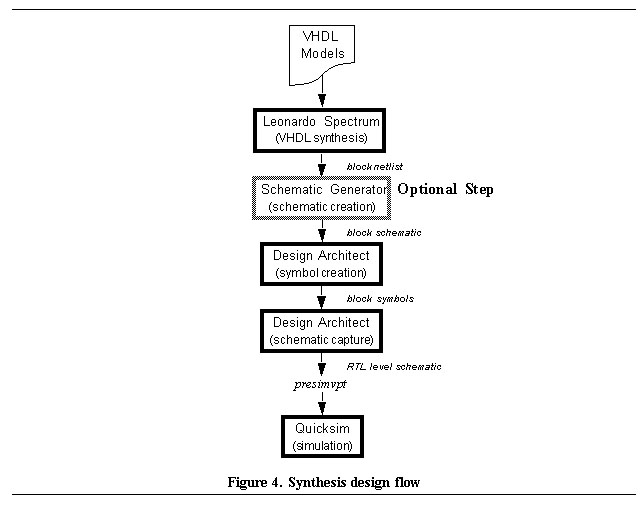

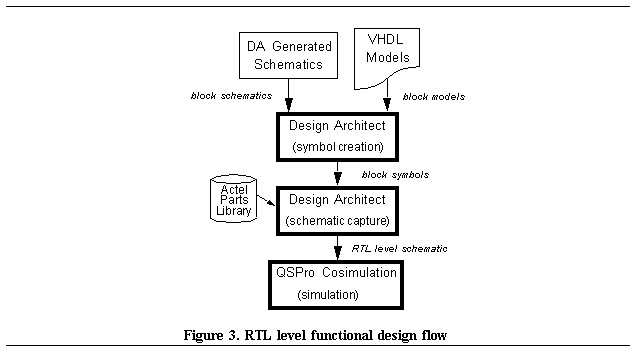

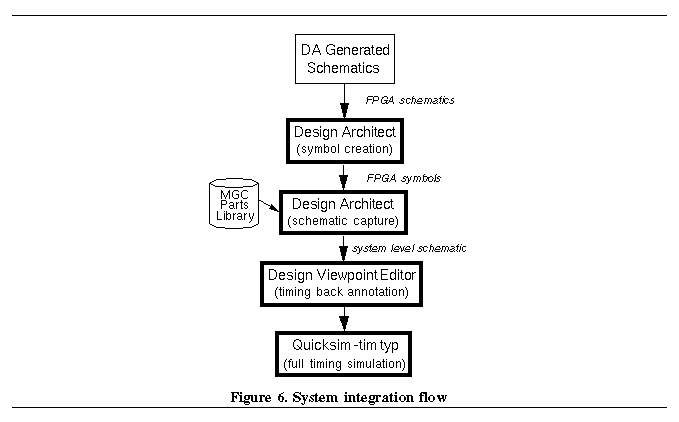

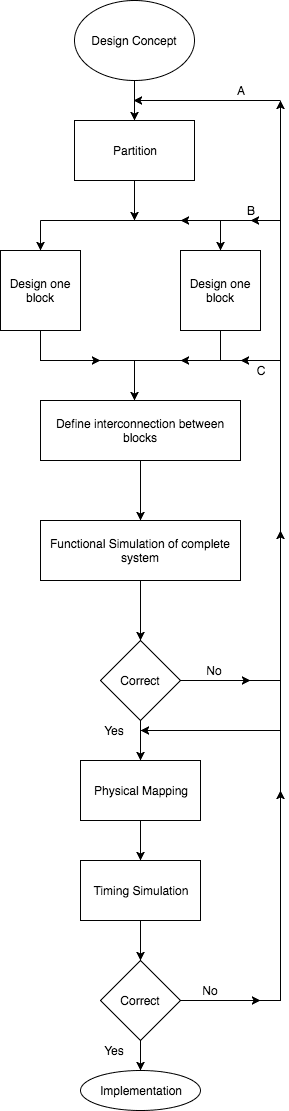

Hdl design flow. The use of flow based design tools in engineering is a reasonably new trend. The company was privately held at that time by dr. Selection of a method depends on the design and designer. The code is analyzed architecturally constrained and scheduled to create a register transfer level rtl hardware design language hdl which is then in turn commonly synthesized to the gate level by the use of a logic synthesis tool.

3 days in this course you create board level schematic designs with design entry hdl. Hdl design house may de personalize personal information by removing personally identifiable characteristics such as name and email address and aggregate data for use in surveys or other business purposes. If the designer wants to deal more with hardware then schematic entry is the better choice. In general as the design flow progresses toward a physically realizable form the design database becomes progressively more laden with technology specific information which cannot be stored in a generic hdl description.

Hdl design house may then use and or share this de personalized information with third parties to improve our services. You follow the design flow by creating a schematic and taking it all the way through board layout. Verilog hdl originated at automated integrated design systems later renamed as gateway design automation in 1985. Although board layout is introduced as part of the front to back flow this.

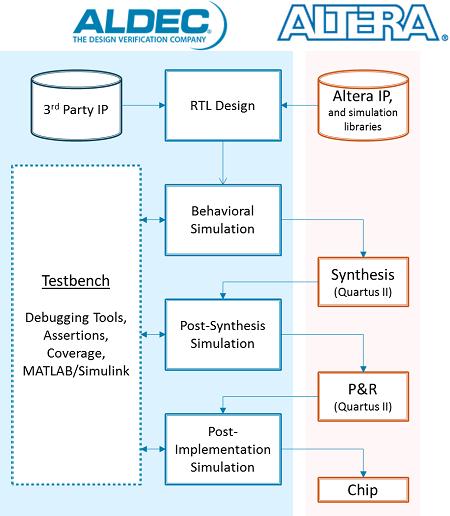

Ema1997 general design flow i 13 of 24 rtl and behavioral design behavioral synthesis a gap between domain specific tools and rtl synthesis tools a higher level of abstraction for the designer to logic synthesis hdl design flow initial model in c or c or simulation vhdl define and test the functional aspects of the design. Silicon vendor supported devices pre compiled simulation libraries ip cores encryption design flow manager integration aldec simulator integration. Hdl designer combines deep analysis capabilities advanced creation editors and complete project and flow management to deliver a powerful hdl design environment that increases the productivity of individual engineers and teams local or remote and enables a repeatable and predictable design process. The use of flow based design tools allows for more holistic system design and faster development.

The starting point of this flow is a high level language such as ansi c c systemc code. Prabhu goel the inventor of the podem test generation algorithm. C to hdl tools and flow have a similar aim but with c or c like programming languages. Verilog hdl was designed by phil moorby who was later to become the chief designer for verilog xl and the first corporate fellow at cadence design systems.